Министерство образования Республики Беларусь Учреждение образования «Витебский государственный университет имени П.М. Машерова» Кафедра инженерной физики

# ИНТЕГРАЛЬНАЯ ЭЛЕКТРОНИКА

Методические рекомендации по выполнению лабораторных работ

> Витебск ВГУ имени П.М. Машерова 2021

УДК 621.382.2/.3(075.8) ББК 32.844.15я73 И73

Печатается по решению научно-методического совета учреждения образования «Витебский государственный университет имени П.М. Машерова». Протокол № 7 от 29.06.2021.

Составители: старшие преподаватели кафедры инженерной физики ВГУ имени П.М. Машерова **Ю.В. Шиёнок, Т.И. Сапелко;** учитель физики и информатики ГУО «Куринская детский садбазовая школа Витебского района имени Героя Советского Союза М.Ф. Сильницкого» **А.А. Людыно**

## Рецензент:

профессор кафедры геометрии и математического анализа ВГУ имени П.М. Машерова, доктор физико-математических наук *Ю.В. Трубников*

**Интегральная электроника :** методические рекомендации **И73** по выполнению лабораторных работ / сост.: Ю.В. Шиёнок, Т.И. Сапелко, А.А. Людыно. — Витебск : ВГУ имени П.М. Машерова, 2021. — 44 с.

Методические рекомендации подготовлены в соответствии с учебной программой для студентов факультета математики и информационных технологий специальности 1-98 01 01-02 Компьютерная безопасность. Содержат теорию, методику выполнения, контрольные вопросы защиты лабораторных работ и список литературы.

Учебное издание предназначено для изучения теоретического материала и отработки практических навыков по дисциплине «Интегральная электроника».

> УДК 621.382.2/.3(075.8) ББК 32.844.15я73

## СОДЕРЖАНИЕ

| ВВЕДЕНИЕ                                                                      | 4  |

|-------------------------------------------------------------------------------|----|

| ЛАБОРАТОРНАЯ РАБОТА № 1. Исследование базовых логических элементов ТТЛ и КМОП | 5  |

| ЛАБОРАТОРНАЯ РАБОТА № 2. Исследование шифраторов и де-<br>шифратора           | 15 |

| ЛАБОРАТОРНАЯ РАБОТА № 3. Исследование мультиплексора и демультиплексора       | 19 |

| ЛАБОРАТОРНАЯ РАБОТА № 4. Исследование сумматоров и компаратора                | 24 |

| ЛАБОРАТОРНАЯ РАБОТА № 5. Исследование триггеров                               | 33 |

| ЛИТЕРАТУРА                                                                    | 43 |

### **ВВЕДЕНИЕ**

Интегральная электроника на сегодняшний день является одной из наиболее бурно развивающихся отраслей современной промышленности. Одной из составных частей данной науки выступает схемотехническая микроэлектроника. На каждом новом этапе развития технологии производства интегральных микросхем (ИМС) создаются принципиально новые методы изготовления структур ИМС, отражающие последние достижения науки.

Возникшая в середине прошлого столетия полупроводниковая электроника стала самым крупным достижением второй половины двадцатого века. К концу столетия полупроводниковая электроника трансформировалась в микроэлектронику. Основные изделия микроэлектроники — интегральные схемы, микропроцессоры, запоминающие устройства — стали основой информационной техники, бытовой электроники, медицины, автомобилестроения, авиации, космической техники и др. Перечень отраслей безграничен, потому что логика развития любой отрасли науки и техники в настоящее время немыслима без использования микрочипов.

Дисциплина «Интегральная электроника» дает возможность познакомиться с будущей специальностью. В учебном издании даются методические указания по выполнению семи лабораторных работ по данному курсу.

### ЛАБОРАТОРНАЯ РАБОТА № 1

### Исследование базовых логических элементов ТТЛ и КМОП

Цель работы: изучение базовых логических элементов «и или не». Оборудование: стенд НТЦ-02.58, комплект перемычек.

## Теория работы

Функционирование любой цифровой системы описывается в двоичной системе счисления, оперирующей только двумя цифрами: нуль (0)и единица (1). В данном случае имеются в виду логические нуль и единица.

Математический аппарат, описывающий поведение цифровых схем, базируется на алгебре логики, или, как ее еще называют по имениавтора — английского математика Джорджа Буля (1815-1864), булевой алгебре. В практических целях первым применил ее американский ученый Клод Шеннон в 1938 году при исследовании электрических цепей сконтактными выключателями.

Предметом рассмотрения алгебры логики является утверждение, которое может быть либо истинным, либо ложным. Принято «истинно» обозначать цифрой 1, «ложно» — цифрой 0.

Простые утверждения, объединенные логическими операциями, образуют сложные утверждения. Если простые утверждения обозначить буквами, например,  $A, B, C, \ldots$ , а сложные буквой F, то, используя законы алгебры логики, можно математически описать сколь угодно сложные логические взаимосвязи и реализующие их цифровыесхемы.

В алгебре логики известны три основные логические операции:

*Логическое умножение* (конъюнкция или операция **И**). Записывается как  $F = A \dot{\mathbf{U}} B$ ,  $F = A \cdot B$ , F = A B, читается — F = A и B. Операция обозначает, что сложное высказывание истинно лишь тогда, когда истинны все простые высказывания.

*Логическое сложение* (дизъюнкция или операция **ИЛИ**). Записывается как  $F = A \dot{\mathsf{U}} B$ , F = A + B, читается -F = A или B. Обозначает, что сложное высказывание истинно, если истинно хотя бы одно из простых высказываний, и тем более, если истинны оба.

*Логическое отрицание* (инверсия или операция **HE**). Записывается  $F = \bar{A}$ , читается -F = «не» A. Операция обозначает, что сложное высказывание истинно, если простое ложно, и наоборот.

Словесное описание приведенных логических операций можно свести к их табличному описанию или заданию (таблица 1.1):

Таблица 1.1 – описание логических операций

|   | иенты<br>сказывания) | Логические операции (булевы функции) |     |   |     |  |  |

|---|----------------------|--------------------------------------|-----|---|-----|--|--|

| A | В                    | И                                    | ИЛИ | H | Œ   |  |  |

|   |                      | $A\grave{\mathrm{U}}B$               | ΑÚB | A | В   |  |  |

| 0 | 0                    | 0                                    | 0   | 1 | _ 1 |  |  |

| 0 | 1                    | 0                                    | 1   | 1 | 0   |  |  |

| 1 | 0                    | 0                                    | 1   | 0 | 1   |  |  |

| 1 | 1                    | 1                                    | 1   | 0 | 0   |  |  |

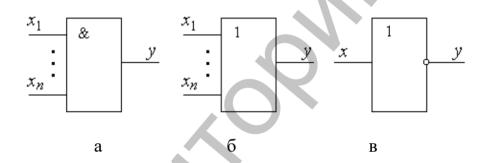

Таким образом, выполнение сколь угодно сложной логической операции может быть сведено к выполнению сочетаний трех вышеперечисленных операций. Следовательно, имея некоторые технические устройства, реализующие операции **И**, **ИЛИ**, **НЕ**, можно построить сколь угодно сложную цифровую систему. Такие устройства называются соответственно логическими элементами (ЛЭ) **И**, **ИЛИ**, **НЕ** и образуют *основной базис* или функционально полную систему (ФПС) логических элементов (рисунок 1.1).

Рисунок 1.1 – Условное обозначение логических элементов на электрических схемах: **И** (а), **ИЛИ** (б), **HE** (в)

Базис считается минимальным, если удаление хотя бы одного из входящих в него ЛЭ, превращает его в функционально неполный. ФПС, состоящая из элементов И, ИЛИ, НЕ, не является минимальной, так как в результате исключения из нее элементов либо И, либо ИЛИ получатся минимальные базисы ИЛИ, НЕ и И, НЕ соответственно, каждый из которых реализуется на двух типах ЛЭ.

В интегральной цифровой электронике широко используются элементы базисов: **ИЛИ** — **HE** (стрелка Пирса  $A \downarrow B$ ), **И** — **HE** (штрих Шеффера  $A \mid B$ ), а также **И** — **ИЛИ** — **HE**, каждый из которых также является функционально полной системой элементов.

## Описание работы

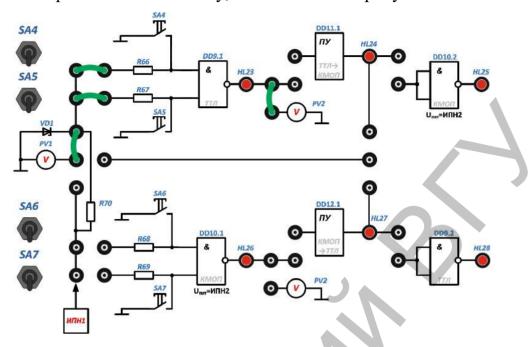

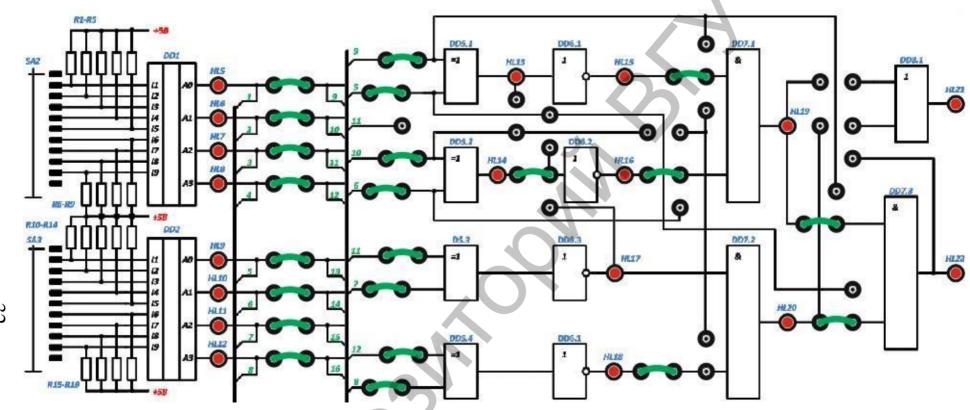

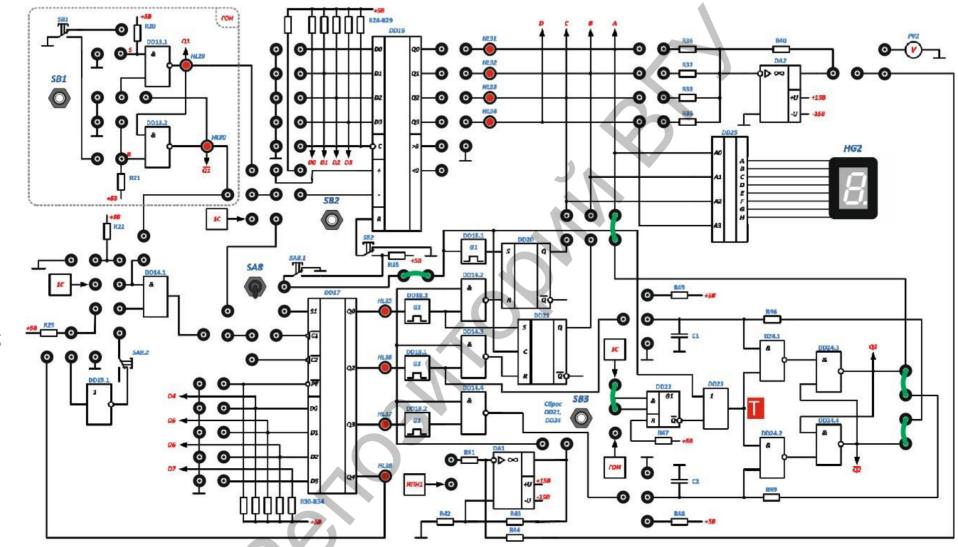

Базовые логические элементы Логический элемент И-НЕ ТТЛ 1. Собрать на панели схему, как показано на рисунке 1.2.

Рисунок 1.2 – Исследование логического элемента И-НЕ ТТЛ

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятся в нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Потенциометром R55 плавно увеличивать напряжение ИПН1 до момента установки навыходе DD9.1 напряжения логического [0] при котором светодиод HL23 гаснет.

- 5. Используя SA4, SA5 изменять сигналы на входах DD9.1 и исследовать все возможные состояния элемента. Данные занести в таблицу 1.2.

- 6. При необходимости повторить опыт при установке другого напряжения ИПН1.

Таблица 1.2 – И-НЕ ТТЛ (DD9.1)

| Сигналы           | Сигналы на выходе Ү |    |           |               |

|-------------------|---------------------|----|-----------|---------------|

| напряжение [1], В | состояние входов    |    | состояние | напряжение, В |

| по PV1            | X1                  | X2 | выхода    | по РV2        |

|                   | 0                   | 0  |           |               |

| _                 | 1                   | 0  |           |               |

|                   | 0                   | 1  |           |               |

|                   | 1                   | 1  |           |               |

7. Выключить питание. Разобрать схему.

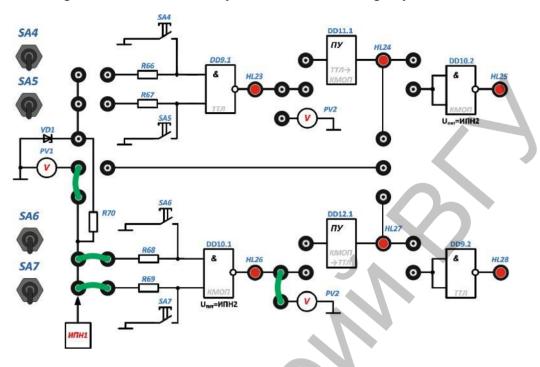

### Логический элемент И-НЕ КПОМ

1. Собрать на панели схему, как показано на рисунке 1.3.

Рисунок 1.3 – Исследование логического элемента И-НЕ КМОП

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятся в нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Потенциометром R56 плавно увеличивать напряжение ИПН2 до момента установки навыходе DD10.1 напряжения 5,0В по прибору PV2.

- 5. Потенциометром R55 плавно увеличивать напряжение ИПН1 до момента установки навыходе DD10.1 напряжения логического [0] при котором светодиод HL26 гаснет.

- 6. Используя SA6, SA7 изменять состояние на входах DD10.1 и исследовать все возможные состояния элемента. Данные занести в таблицу 1.3.

- 7. При необходимости повторить опыт при установке других напряжений ИПН1 и ИПН2.

Таблица 1.3 – И-НЕ КМОП (DD10.1)

| Сигналы на входах |             | Сигналы на выходе Ү |        |               |  |

|-------------------|-------------|---------------------|--------|---------------|--|

| напряжение [1], В | состояние і | состояние входов    |        | напряжение, В |  |

| по PV1            | X1 X2       |                     | выхода | по РV2        |  |

|                   | 0           | 0                   |        |               |  |

|                   | 1           | 0                   |        | <b>A</b>      |  |

|                   | 0           | 1                   |        |               |  |

|                   | 1           | 1                   |        |               |  |

8. Выключить питание. Разобрать схему. Справочные данные. Тип микросхемы DD9: K155ЛA3.

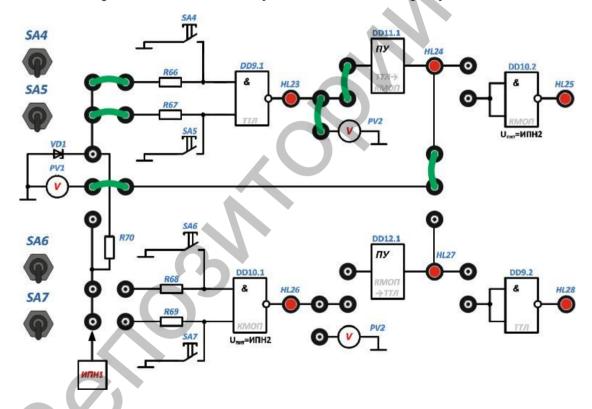

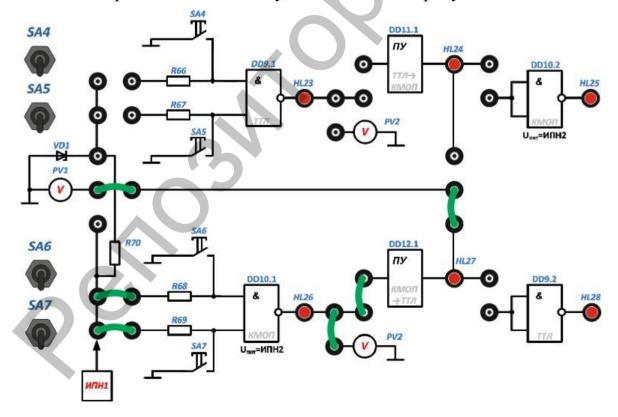

Преобразователи уровней логических сигналов Преобразователь уровня ТТЛ в КМОП

1. Собрать на панели схему, как показано на рисунке 1.4.

Рисунок 1.4 – Исследование преобразователя уровня ТТЛ в КМОП

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятся в нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Потенциометром R56 плавно увеличивать напряжение ИПН2 до момента установки навыходе DD11.1 напряжения 5,0В по прибору PV1.

- 5. Потенциометром R55 плавно увеличивать напряжение ИПН1 до момента установки навыходе DD9.1 напряжения логического [0] при котором светодиод HL23 гаснет.

- 6. Исследовать зависимость состояния и напряжения на выходе DD11.1 от состояния на еговходе (состояние на входе изменять используя SA4, SA5). Данные занести в таблицу 1.4.

- 7. Повторить опыт при установке другого напряжения питания DD11.1 (регулируя ИПН2).

Таблица 1.4 – ТТЛ -> КМОП (DD11.1)

| Сигна.    | л на входе              | Сигнал на выходе |               |  |  |  |

|-----------|-------------------------|------------------|---------------|--|--|--|

| состояние | состояние напряжение, В |                  | напряжение, В |  |  |  |

| 0         |                         |                  |               |  |  |  |

| 1         |                         |                  |               |  |  |  |

8. Выключить питание. Разобрать схему. Справочные данные. Тип микросхемы DD11: K564ПУ8.

## Преобразователь уровня КМОП в ТТЛ

1. Собрать на панели схему, как показано на рисунке 1.5.

Рисунок 1.5 – Исследование преобразователя уровня КМОП в ТТЛ

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятся в нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Потенциометром R56 плавно увеличивать напряжение ИПН2 до момента установки навыходе DD10.1 напряжения 5,0В по прибору PV2.

- 5. Потенциометром R55 плавно увеличивать напряжение ИПН1 до момента установки навыходе DD10.1 напряжения логического [0] при котором светодиод HL26 гаснет.

- 6. Исследовать зависимость состояния и напряжения на выходе DD12.1 от состояния на еговходе (состояние на входе изменять используя SA6, SA7). Данные занести в таблицу 1.5.

- 7. Повторить опыт при установке других напряжений ИПН1 и ИПН2.

Таблица 1.5 –КМОП -> ТТЛ (DD12.1)

| Сигна                   | л на входе | Сигнал на выходе |               |  |  |  |

|-------------------------|------------|------------------|---------------|--|--|--|

| состояние напряжение, В |            | состояние        | напряжение, В |  |  |  |

| 0                       |            |                  |               |  |  |  |

| 1                       |            |                  |               |  |  |  |

8. Выключить питание. Разобрать схему. Справочные данные. Тип микросхемы DD12: К564ПУ4.

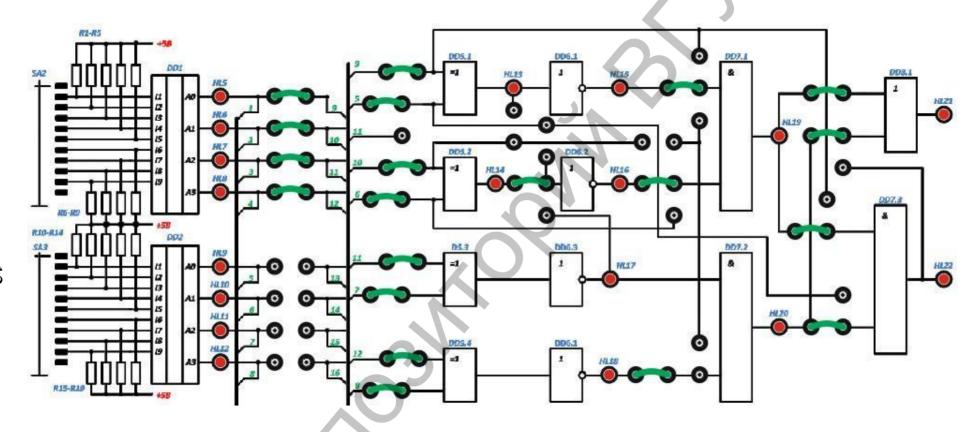

### Логические элементы

1. Собрать на панели схему, как показано на рисунке 1.6.

Рисунок 1.6 – Исследование логических элементов

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

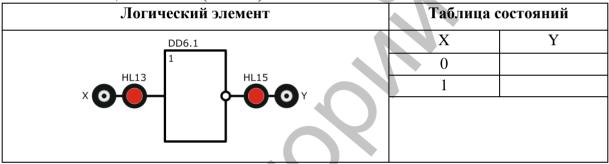

### Логический элемент НЕ

4. Изменяя логические уровни линий 5, 9 (изменение производить сменой комбинаций положений галетных переключателей SA2, SA3) исследовать DD6.1 путем составления таблицы состояний логического элемента. Состояния входа и выхода отслеживать по светодиодам HL13, HL15. Данные занести в таблицу 1.6.

Таблица 1.6 – HE (DD6.1)

### Логический элемент И

5. Изменяя логические уровни линий 5, 9, 6, 10 (изменение производить сменойкомбинаций положений галетных переключателей SA2, SA3) исследовать DD7.1 путем составления таблицы состояний логического элемента. Состояния входов и выхода отслеживать по светодиодам HL15, HL16, HL19. Данные занести в таблицу 1.7.

Таблица 1.7 – И (DD7.1)

| Логический элемент | Таблица состояний |    |   |  |

|--------------------|-------------------|----|---|--|

| DD7.1              | X1                | X2 | Y |  |

| X1 0-4L15 & HL19   | 0                 | 0  |   |  |

|                    | 0                 | 1  |   |  |

| HL16               | 1                 | 0  |   |  |

| ^2                 | 1                 | 1  |   |  |

|                    |                   |    |   |  |

### Логический элемент ИЛИ

6. Изменяя логические уровни линий 5...12 (изменение производить сменой комбинаций положений галетных переключателей SA2, SA3) исследовать DD8.1 путем составления таблицы состояний логического элемента. Состояния входов и выхода отслеживать по светодиодам HL19, HL20, HL21. Данные занести в таблицу 1.8.

Таблица 1.8 –ИЛИ (DD8.1)

| Логический элемент | Таблица состояний |    |   |  |

|--------------------|-------------------|----|---|--|

| DD8.1<br>HL19      | X1                | X2 | Y |  |

| X1 O               | 0                 | 0  |   |  |

| HL21               | 0                 | 1  |   |  |

| HL20               | 1                 | 0  |   |  |

|                    | 1                 | 1  |   |  |

|                    |                   |    |   |  |

Логический элемент исключающее ИЛИ

- 7. Изменяя логические уровни линий 5, 9 (изменение производить сменой комбинаций положений галетных переключателей SA2, SA3) исследовать DD5.1 путем составления таблицы состояний логического элемента. Состояния входов и выхода отслеживать по светодиодам HL5, HL9, HL13. Данные занести в таблицу 1.9.

- 8. Выключить питание. Разобрать схему.

Таблица 1.9 – Исключающее ИЛИ (DD5.1)

| Логический элемент | Таблица состояний |    |   |  |

|--------------------|-------------------|----|---|--|

| DD5.1              | X1                | X2 | Y |  |

| X1                 | 0                 | 0  |   |  |

|                    | 0                 | 1  |   |  |

|                    | 1                 | 0  |   |  |

|                    | 1                 | 1  |   |  |

## Контрольные вопросы

- 1. Дайте определение понятию «логическая операция».

- 2. Какие логические операции Вы знаете, дайте им определения.

- 3. Нарисуйте условные обозначения логических элементов на электронных схемах.

- 4. Запишите таблицу истинности для логического элемента исключающее ИЛИ.

### ЛАБОРАТОРНАЯ РАБОТА № 2

### Исследование шифраторов и дешифратора

Цель работы: изучить действие дешифраторов, шифраторов и преобразователей кодов.

Оборудование: стенд НТЦ-02.58, комплект перемычек

### Теория работы

**Дешифратор.** Комбинационное устройство, позволяющее преобразовать n-разрядный двоичный код в позиционный  $2^n$ -разрядный код.Имеет n входов и  $2^n$  или меньше выходов. В зависимости от входного набора сигнал 1 появится только на одном определенном выходе, а на всех остальных выходах будут сигналы 0.

Таблица истинности полного дешифратора, например, на три входа имеет вид (таблица 2.1):

Таблица 2.1 – Таблица истинности полного дешифратора на три входа

| Номер           | В                     | ходы                  |       | Выходы |            |            |    |            |            | , ,        |            |

|-----------------|-----------------------|-----------------------|-------|--------|------------|------------|----|------------|------------|------------|------------|

| входного набора | <i>x</i> <sub>3</sub> | <i>x</i> <sub>2</sub> | $x_1$ | yo     | <b>y</b> 1 | <b>y</b> 2 | у3 | <b>y</b> 4 | <b>y</b> 5 | <b>y</b> 6 | <b>y</b> 7 |

| 0               | 0                     | 0                     | 0     | 1      | 0          | 0          | 0  | 0          | 0          | 0          | 0          |

| 1               | 0                     | 0                     | 1     | 0_     | 1          | 0          | 0  | 0          | 0          | 0          | 0          |

| 2               | 0                     | 1                     | 0     | 0      | 0          | 1          | 0  | 0          | 0          | 0          | 0          |

| 3               | 0                     | 1                     | 1     | 0      | 0          | 0          | 1  | 0          | 0          | 0          | 0          |

| 4               | 1                     | 0                     | 0     | 0      | 0          | 0          | 0  | 1          | 0          | 0          | 0          |

| 5               | 1                     | 0                     | 1     | 0      | 0          | 0          | 0  | 0          | 1          | 0          | 0          |

| 6               | 1                     | 1                     | 0     | 0      | 0          | 0          | 0  | 0          | 0          | 1          | 0          |

| 7               | 1                     | 1                     | 1     | 0      | 0          | 0          | 0  | 0          | 0          | 0          | 1          |

По способу реализации дешифраторы могут быть линейные, прямоугольные и пирамидальные.

Более совершенными являются пирамидальные дешифраторы, относящиеся к многоступенчатым структурам и содержащие ряд логических элементов для выделения общих частей функций.

В ниже следующей таблице дана сравнительная оценка линейных, пирамидальных и прямоугольных дешифраторов по аппаратным затратам  $N_{\rm ЛЭ}$  в пересчете на 2-входные ЛЭ для m-разрядного входного кода (таблица 2.2).

Таблица 2.2 — Сравнительная оценка линейных, пирамидальных и прямоугольных дешифраторов по аппаратнымзатратам

| Тип дешифратора |               | m |    |    |     |     |     |      |  |  |

|-----------------|---------------|---|----|----|-----|-----|-----|------|--|--|

|                 |               | 2 | 3  | 4  | 5   | 6   | 7   | 8    |  |  |

|                 | Линейный      | 4 | 16 | 48 | 128 | 320 | 768 | 1792 |  |  |

| Νπэ             | Пирамидальный | 4 | 12 | 28 | 60  | 124 | 252 | 508  |  |  |

|                 | Прямоугольный | 4 | 12 | 24 | 48  | 88  | 164 | 304  |  |  |

Как видно из таблицы 2.2, преимущества многоступенчатых дешифраторов заметно нарастают с увеличением *m*. В специализированных ИС тем не менее предпочтение часто отдают более простым линейным (одноступенчатым) дешифраторам, обладающим к тому же повышенным быстродействием.

**Шифратор.** Это комбинационное устройство, преобразующее управляющий сигнал на одном из входов в соответствующий двоичный код.

Таблица 2.3 – таблица истинности шифратора на четыре входа и два выхода

| Номер набора | $x_1$ | $x_2$ | <i>x</i> <sub>3</sub> | <i>X</i> 4 | <i>y</i> <sub>1</sub> | <i>y</i> 2 |

|--------------|-------|-------|-----------------------|------------|-----------------------|------------|

| 0            | 0     | 0     | 0                     | 1          | 0                     | 0          |

| 1            | 0     | 0     | 1                     | 0          | 0                     | 1          |

| 2            | 0     | 1     | 0                     | 0          | 1                     | 0          |

| 3            | 1     | 0     | 0                     | 0          | 1                     | 1          |

Наибольшее применение шифраторы находят в цифровых устройствах ввода информации с пультов управления для преобразования десятичных чисел в двоичный код. При нажатии на клавишу на один их входов шифратора подается логическая единица (на остальные – логические нули), на выходе формируется соответствующий двоичный код.

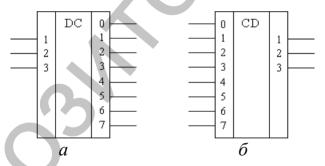

Условное обозначение дешифратора и шифратора приведено на рисунке 2.1:

Рисунок 2.1 – Условное обозначение: a – дешифратор;  $\delta$  – шифратор

**Преобразователи кодов.** Это устройства для автоматическогоизменения по заданному алгоритму соответствия между входным и выходным кодами без изменения их смыслового содержания.

По-другому, преобразователь кода представляет собой устройство с m входами и n выходами, взаимно и однозначно преобразующее входные слова из некоторого алфавита  $\{X_1, X_2, ..., X_p\}$  и выходные слова другого алфавита  $\{Y_1, Y_2, ..., Y_u\}$ .

Задача преобразования кодов возникает прежде всего в связи с необходимостью сведения цифровых устройств с разнообразными способами кодирования в единую систему.

Для преобразования параллельных двоичных кодов можно построить достаточно простые преобразователи на комбинационных логических схемах. Однако на практике это часто осуществляется алгоритмическим путем, используя запоминающие устройства.

## Описание работы

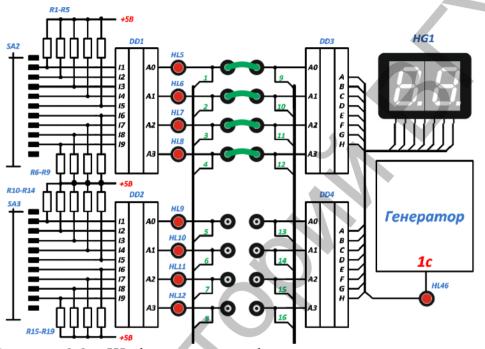

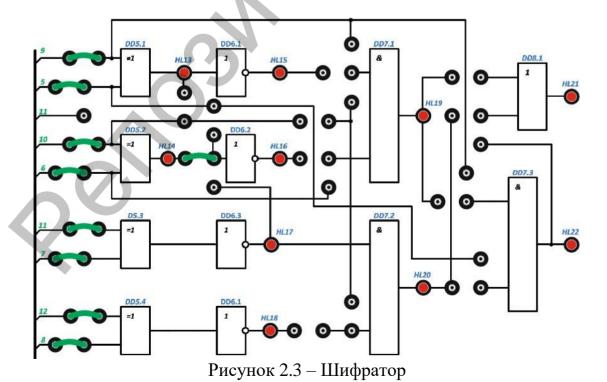

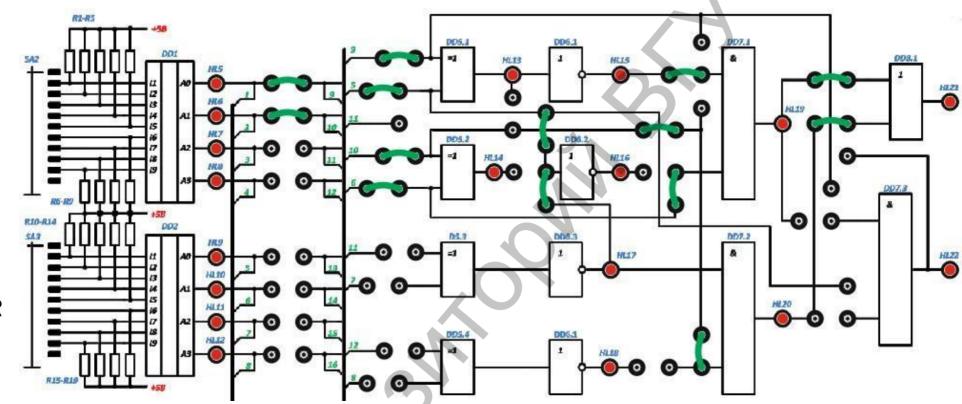

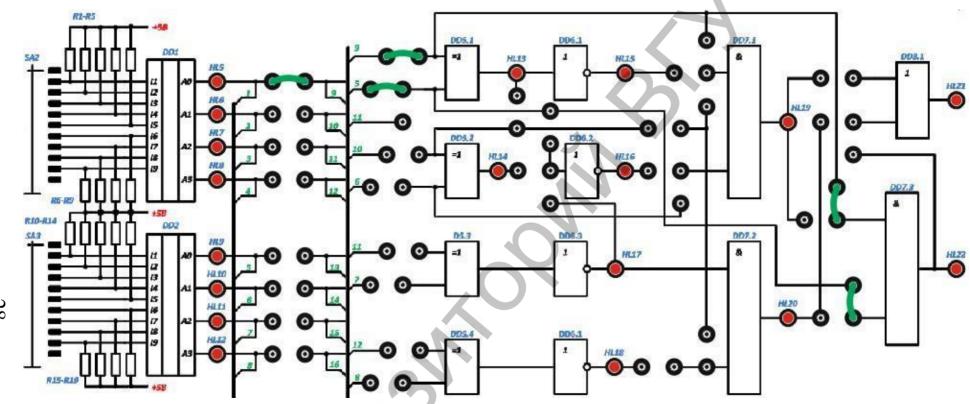

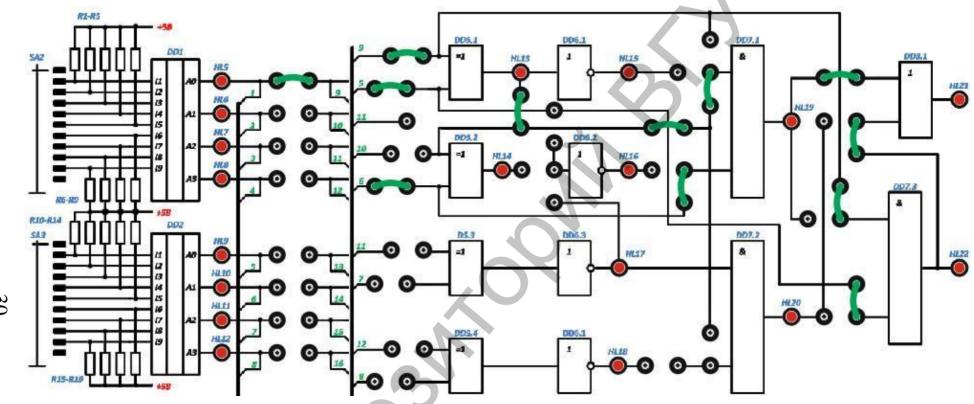

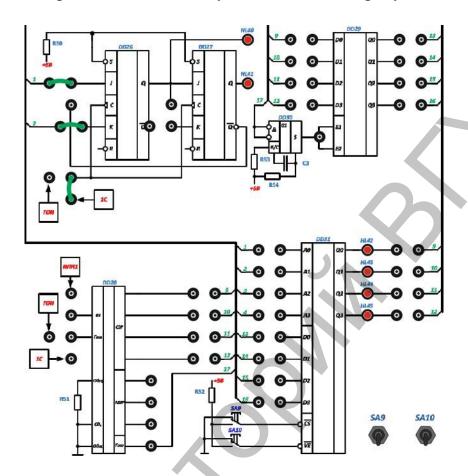

1. Собрать на панели схему, как показано на рисунках 2.2 и 2.3.

Рисунок 2.2 – Шифратор и дешифратор в интегральном исполнении

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя логические уровни линий 9...12 (изменение производить сменой положения галетного переключателя SA2) исследовать работу шифратора в интегральном исполнении (DD1), дешифратора в интегральном исполнении (DD3) и шифратора собранного на логических элементах DD5, DD6 путем составления их таблиц состояний. Состояния входов DD1 отслеживать по положению SA2, состояние выходов DD1 и входов DD3 отслеживать по светодиодам HL5...HL8, состояния выходов DD3 отслеживать по индикатору HG1. Состояние на входе сборного шифратора DD5, DD6 соответствует DD1, состояние на выходе сборного шифратора DD5, DD6 отслеживать по светодиодам HL15...HL18. Данные занести в таблицу 2.4.

Таблица 2.4 – Выходные данные

|       | тиолици 2.4 Выходиые динные |     |        |                        |                  |       |       |        |       |

|-------|-----------------------------|-----|--------|------------------------|------------------|-------|-------|--------|-------|

| Входы | Выходы (A) DD1              |     |        | Число                  | Выходы шифратора |       |       | a      |       |

| DD1   | входы (A) DD3               |     | на HG1 | собранного на DD5, DD6 |                  |       | DD6   |        |       |

| Ii    | A0                          | A1  | A2     | A3                     |                  | HL15  | HL16  | HL17   | HL18  |

|       | AU                          | 711 | 112    | 113                    |                  | IILIJ | IILIU | 111217 | IILIO |

| IO    |                             |     |        |                        |                  |       |       |        |       |

| I1    |                             |     |        |                        |                  |       |       |        |       |

| I2    |                             |     | 1      | 7                      |                  |       |       |        |       |

| I3    |                             |     |        |                        |                  |       |       |        |       |

| I4    |                             |     |        |                        |                  |       |       |        |       |

| I5    |                             |     |        |                        |                  |       |       |        |       |

| I6    |                             |     | )      |                        |                  |       |       |        |       |

| I7    |                             |     |        |                        |                  |       |       |        |       |

| I8    |                             |     |        |                        |                  |       |       |        |       |

| I9    |                             |     |        |                        |                  |       |       |        |       |

5. Выключить питание. Разобрать схему.

Справочные данные.

Тип микросхемы DD1: К155ИВ3. Тип микросхемы DD3: К514ИД2.

## Контрольные вопросы

- 1. Дайте определение понятию «шифратор».

- 2. Опишите принцип работы шифратора.

- 3. Что представляет собой понятие «дешифратора» в технике?

- 4. Дайте определение преобразователя кодов?

### ЛАБОРАТОРНАЯ РАБОТА № 3

### Исследование мультиплексора и демультиплексора

Цель работы: изучить устройство мультиплексора и демультиплексора.

Оборудование: НТЦ-02.58, комплект перемычек.

### Теория работы

**Демультиплексоры** (распределители). Устройства, передающие сигнал, поступивший на его вход x, на один из S выходов в зависимостиот управляющего сигнала (УС), заданного двоичным кодом.

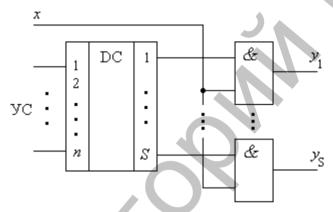

Структура демультиплексора имеет вид, представленный на рисунке 3.1

Рисунок 3. 1 – Структура демультиплексора

Демультиплексоры по своей логике работы близки к дешифраторам. Если на вход x подать логическую единицу, то показанный на рисунке 3.1 демультиплексор превращается в дешифратор. Поэтому некоторые промышленно выпускаемые дешифраторы могут выполнять функции демультиплексоров.

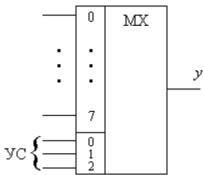

**Мультиплексор.** Устройство для коммутации информации, поступающей по нескольким входным каналам, на один выходной канал в зависимости от управляющего сигнала, заданного двоичным кодом.

Если мультиплексор имеет n-разрядный управляющий сигнал, то количество коммутируемых входов составит —  $2^n$  (рисунок 3.2).

Рисунок 3.2 – Условное обозначение мультиплексора

### Описание работы

Мультиплексор

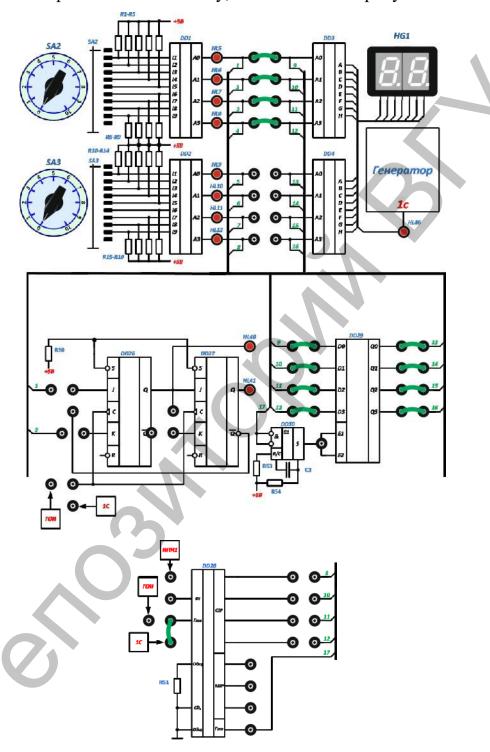

- 1. Собрать на панели схему, как показано на рисунке 3.3.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя логические уровни линий 5, 6, 10 (изменение производить сменой положений галетных переключателей SA2, SA3) исследовать работу предлагаемой схемымультиплексора имеющего два входа данных и один переключающий (адресный) вход путем составления таблицы состояний. Состояния входов данных отслеживать по светодиодам HL6, HL10, состояние адресного входа отслеживать по светодиоду HL9, состояние выхода по светодиоду HL21. Данные занести в таблицу 3.1.

- 5. Выключить питание. Разобрать схему.

Таблица 3.1 – Мультиплексор, собранный на DD5, DD6, DD7, DD8

| Tuestingue 3.1 Till interfere epi, ecopatinisti na 223, 220, 7, 220 |         |        |       |  |  |  |

|---------------------------------------------------------------------|---------|--------|-------|--|--|--|

| Bxc                                                                 | оды     | Адрес  | Выход |  |  |  |

| X1                                                                  | X2      | A      | Y     |  |  |  |

| line_6                                                              | line_10 | line_5 | _     |  |  |  |

| HL10                                                                | HL6     | HL9    | HL21  |  |  |  |

| 0                                                                   | 0       | 0      |       |  |  |  |

| 0                                                                   | 1       | 0      |       |  |  |  |

| 1                                                                   | 0       | 0      |       |  |  |  |

| 1                                                                   | 1       | 0      |       |  |  |  |

| 0                                                                   | 0       | 1      |       |  |  |  |

| 0                                                                   | 1       | 1      |       |  |  |  |

| 1                                                                   | 0       | 1      |       |  |  |  |

| 1                                                                   | 1       | 1      |       |  |  |  |

Рисунок 3.3 – Мультиплексор

### Демультиплексор

- 1. Собрать на панели схему, как показано на рисунке 3.4.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя логические уровни линий 5, 9 (изменение производить сменой положений галетных переключателей SA2, SA3) исследовать работу предлагаемой схемыдемультиплексора имеющего один вход данных и один переключающий (адресный) вход путем составления таблицы состояний. Состояния входа данных отслеживать по светодиоду HL5, состояние адресного входа отслеживать по светодиоду HL9, состояние выходов по светодиодам HL19, HL22. Данные занести в таблицу 3.2.

- 5. Выключить питание. Разобрать схему.

Таблица 3.2 – Демультиплексор, собранный на DD5, DD6, DD7

| Вход   | Адрес  |      | , , <u> </u> |

|--------|--------|------|--------------|

| X      | A      | Y1   | Y2           |

| line_9 | line_5 | -    | -            |

| HL5    | HL9    | HL19 | HL22         |

| 0      | 0      |      |              |

| 0      | 1      |      |              |

| 1      | 0      |      |              |

| 1      | 1      |      |              |

## Контрольные вопросы

- 1. Дайте определение демультиплексора.

- 2. Опишите принцип работы демультиплексора.

- 3. Дайте определение мультиплексора.

- 4. Опишите принцип работы мультиплексора.

Рисунок 3.4 – Демультиплексор

### ЛАБОРАТОРНАЯ РАБОТА № 4

### Исследование сумматоров и компаратора

Цель работы: изучить работу сумматоров и компоратора.

Оборудование: НТЦ-02.58, комплект перемычек.

## Теория работы

Сумматоры

Сумматорами называются цифровые функциональные устройства, предназначенные для выполнения операции сложения чисел, представленных в различных кодах.

По характеру действия сумматоры подразделяются на комбинационные, не имеющие элементов памяти, и накапливающие — запоминающие результаты вычислений при снятии входных сигналов.

В дальнейшем будут рассматриваться только комбинационные сумматоры, на основе которых выполняется большинство суммирующих ИС.

**Сумматор по модулю два.** Это устройство с двумя входами  $(a \ u \ b)$ , на выходе у которого сигнал «1» появляется только в том случае, когда на входах действуют противоположные сигналы, т. е. «0» и «1». Сумматор не обладает памятью, а его таблица истинности представлена в таблице 4.1.

Таблица 4.1 – Таблица истинности сумматора по модулю 2

| X1 | X2 | Y |

|----|----|---|

| 0  | 0  | 0 |

| 0  |    | 1 |

| 1  | 0  | 1 |

| 1  | 1  | 0 |

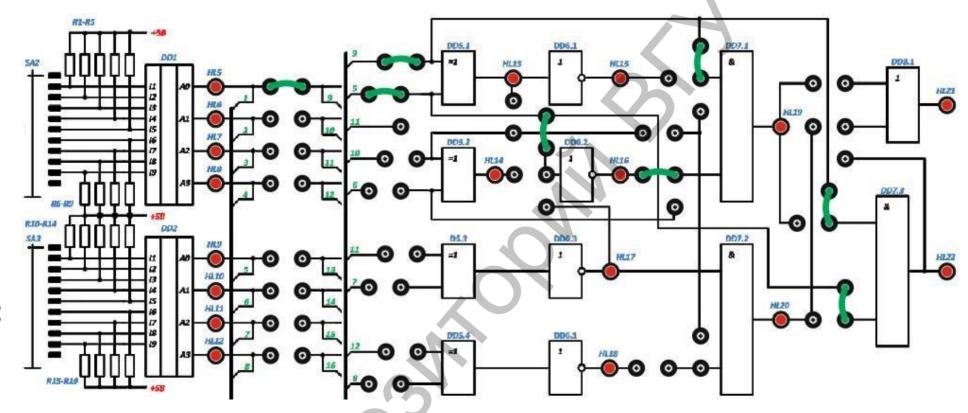

Название «по модулю два» этот сумматор получил потому, что y соответствует значению младшего разряда при суммировании одноразрядных двоичных чисел A и B. Построим в базисе  $\mathbf{И}$ — $\mathbf{HE}$  схему сумматора по модулю два.

Для этого преобразуем его логическое уравнение, применив к нему последовательно двойное отрицание и теорему де Моргана.

Тогда логическая схема сумматора примет вид, представленный на рисунке 4.1.

Рисунок 4.1 — Реализация сумматора по модулю два: a — принципиальная схема;  $\delta$  — функциональная схема

**Полусумматор.** Обеспечивает операцию сложения двух одноразрядных двоичных чисел a и b. Так как при a=1 и b=1 получается перенос единицы в следующий разряд, полусумматор должен иметь два выхода: с одного снимается сигнал суммы по модулю два, а с другого соответственно — сигнал переноса. Таблица истинности полусумматора представлена в таблице 4.2.

Таблица 4.2 – Таблица истинности полусумматора

| $\mathbf{A_0}$ | $B_0$ | $S_0$ | $\mathbf{P}_{0}$ |

|----------------|-------|-------|------------------|

| 0              | 0     | 0     | 0                |

| 0              | 1     | 1     | 0                |

| 1              | 0     | 1     | 0                |

| 1              | 1     | 0     | 1                |

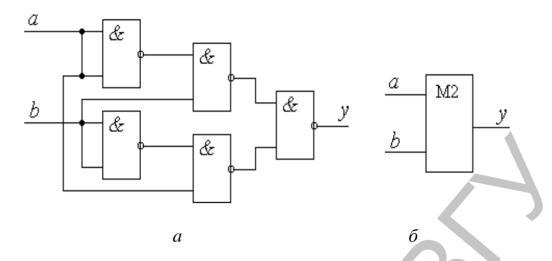

Реализация полусумматора в базисе **И–НЕ** представлена на рисунке 4.2.

Рисунок 4.2 — Схема полусумматора: a — реализация в базисе **И—НЕ**;  $\delta$  — условное обозначение

Условное обозначение полусумматора на схемах — HS (halfsum — полусумма), а полного сумматора — SM.

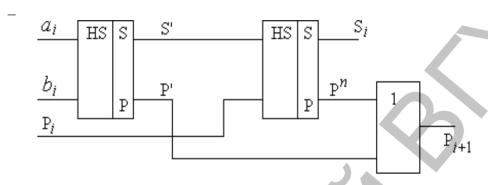

**Полный сумматор.** Это устройство для сложения трех одноразрядных двоичных чисел a, b, c, где c — сигнал переноса из предыдущего младшего разряда. Имеет два выхода S (сумма) и P (перенос). Полный сумматор можно построить из двух полусумматоров (рисунок 4.3).

Рисунок 4.3 – Полный сумматор

На основе полного сумматора можно построить суммирующие устройства параллельного или последовательного действия для сложения многоразрядных двоичных чисел.

В цифровой схемотехнике операцию вычитания обычно заменяют сложением уменьшаемого с вычитаемым, представленным в дополнительном коде, поэтому вычитатели могут быть выполнены на основе сумматоров.

### Цифровые компараторы.

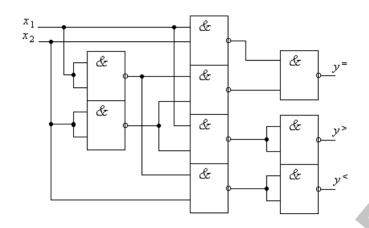

Компаратором называется устройство сравнения кодов нескольких чисел. В общем случае компаратор параллельных кодов двух *т*-разрядных двоичных чисел представляет собой комбинационную схему с 2*т* входами и тремя выходами («равно», «больше», «меньше»). При поступлении на входы кодов двух сравниваемых чисел сигнал логической единицы, в зависимости от результатов сравнения, появляется только на одном из выходов. В некоторых случаях компаратор может иметь менее трех выходов.

Одноразрядный компаратор имеет два входа на которые одно- временно поступают одноразрядные двоичные числа  $x_1$  и  $x_2$ , и три выхода (=, >, <).

Реализация такого компаратора в базисе **И–НЕ** приводит к следующей схеме на рисунке 4.4:

Рисунок 4.4 – Одноразрядный компаратор двоичных чисел

Многоразрядные компараторы обычно выполняют на базе одноразрядных. При этом используется принцип последовательного сравнения разрядов многоразрядных чисел, начиная с их старших разрядов, так как уже на этом этапе, если  $x_{1m}$   $x_{2m}$ , задача может быть решена однозначно, и сравнение следующих за старшими разрядов не потребуется.

### Описание работы

### Полусумматор

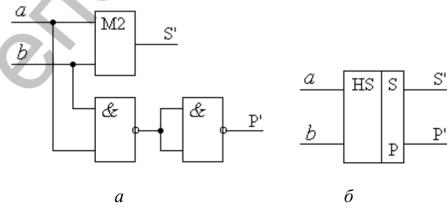

- 1. Собрать на панели схему, как показано на рисунке 4.5.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятся в нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя логические уровни линий 5, 9 (изменение производить сменой положений галетных переключателей SA2, SA3) исследовать работу предлагаемой схемыполусумматора имеющего два входа данных путем составления таблицы состояний. Состояния входов данных отслеживать по светодиодам HL5, HL9, результат работы отслеживать по светодиодам HL13, HL22. Данные занести в таблицу 4.3.

- 5. Выключить питание. Разобрать схему.

Таблица 4.3 – Полусумматор, собранный на DD5, DD7

| Bxo    | ды     | Выходы |      |  |

|--------|--------|--------|------|--|

| X1 X2  |        | S      | C    |  |

| line_9 | line_5 | _      | _    |  |

| HL5    | HL9    | HL13   | HL22 |  |

| 0      | 0      |        |      |  |

| 0      | 1      |        |      |  |

| 1      | 0      |        |      |  |

| 1      | 1      |        |      |  |

Рисунок 4.5 – Полусумматор

### Двоичный сумматор

- 1. Собрать на панели схему, как показано на рисунке 4.6.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя логические уровни линий 5, 9 (изменение производить сменой положений галетных переключателей SA2, SA3) исследовать работу предлагаемой схемысумматора имеющего два входа данных (X) и вход операции (P) путем составления таблицы состояний. Состояния входов отслеживать по светодиодам HL5, HL9, HL10 результат работы отслеживать по светодиодам HL14, HL21. Данные занести в таблицу 4.4.

Таблица 4.4 – Сумматор, собранный на DD5, DD7, DD8

| ·      | <u>4 — Сумматор, с</u><br>Входы | Выходы |      |      |

|--------|---------------------------------|--------|------|------|

| X1     | X2                              | P      | S    | С    |

| line_9 | line_5                          | line_6 | _    | _    |

| HL5    | HL9                             | HL10   | HL14 | HL21 |

| 0      | 0                               | 0      |      |      |

| 0      | 1                               | 0      |      |      |

| 1      | 0                               | 0      |      |      |

| 1      | 1                               | 0      |      |      |

| 0      | 0                               | 1      |      |      |

| 0      | 1                               | 1      |      |      |

| 1      | 0                               | 1      |      |      |

| 1      | 1                               | 1      |      |      |

5. Выключить питание. Разобрать схему.

Рисунок 4.6 – Сумматор

### Компаратор двух чисел

- 1. Собрать на панели схему, как показано на рисунке 4.7.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя положение галетного переключателя SA2 задать первое число (слово) для сравнения. Значение числа отслеживать по светодиодам HL5...HL8. Изменяя положение галетного переключателя SA3 задать второе число (слово) для сравнения. Значение числа отслеживать по светодиодам HL9...HL12. Значение слов также можно контролировать по индикатору HG1. Результат сравнения двух чисел отслеживать по светодиоду HL22.

- 5. Выключить питание. Разобрать схему.

### Контрольные вопросы

- 1. Дайте определение понятию «сумматорами», его применение.

- 2. Что представляет сбой понятие «сумматор по модулю два»?

- 3. Перечислите основные функции и характеристики полусумматора.

Рисунок 4.7 – Компаратор

### ЛАБОРАТОРНАЯ РАБОТА № 5

### Исследование триггеров

Цель работы: изучить работу триггеров.

Оборудование: НТЦ-02.58, комплект перемычек.

### Теория работы

*Триггером* называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое.

Можно выделить две основные области их применения: формирование импульсов и работу в качестве элементарных автоматов цифровых устройств.

Как формирователи, триггеры позволяют получать стандартные по амплитуде прямоугольные импульсы с малой длительностью фронта и среза, практически не зависящей от скорости измененияуправляющего сигнала. В роли цифровых автоматов с двумя внутренними состояниями различные типы триггеров выполняют функции ячеек памяти, каскадов задержки, пересчетных ячеек и т.д.

Триггер, как элементарный конечный автомат, характеризуется следующими свойствами:

- число внутренних состояний два (единица и нуль), что соответствует одной внутренней переменной, обозначаемой для триггеров буквой O;

- число выходных переменных y одно, значение переменной y совпадает со значением Q;

- число входных переменных x зависит от типа триггера.

Наряду с выходом Q, называемым прямым, триггер имеет и инверсный выход Q . Состояние триггера определяется значением его прямого выхода.

Все известные на сегодняшний день триггеры по функциональному признаку можно разделить на четыре основных типа:

- *RS*-триггеры триггеры с двумя установочными входами;

- Т-триггеры триггеры с одним счетным входом;

- универсальные триггеры с несколькими входами.

Как и любые цифровые автоматы, триггеры могут быть асинхронными и синхронными.

Различают также триггеры со статическими и динамическими входами. Входы, управляемые потенциалами (уровнями напряжений), называются *статическими* (включая и входы синхронизации).

Причем, если триггер переключается сигналами логической единицы, то его называют триггером с *прямым управлением*, в противном случае — триггером с *инверсным управлением*.

Возможны следующие состояния триггера, в зависимости от комбинации входных сигналов:

- $S^n$ ,  $R^n = 0$ , сигнал на выходе может быть  $Q^{n+1} = 1$  или  $Q^{n+1} = 0$ , что соответствует нейтральному состоянию (режим хранения информации);

- $S^n=1, R^n=0, Q^{n+1}=1$  установка триггера в единичное состояние;

- $S^n = 0, R^n = 1, Q^{n+1} = 0$  установка в нулевое состояние;

- $S^n = 1$ ,  $R^n = 1$  состояние не определено. Если затем входная комбинация станет  $S^n = 0$ ,  $R^n = 0$ , то триггер с равной вероятностью может установиться или в нулевое, или в единичное состояние, поэтому входная комбинация  $S^n = 1$ ,  $R^n = 1$  недопустима.

При синтезе устройств на триггерах возникает задача определения требуемых входных комбинаций для перехода триггера из одного (заданного) состояния  $Q^n$  в другое (требуемое)  $Q^{n+1}$ .

Эту задачу удобно решать с помощью таблицы, называемой матрицей переходов.

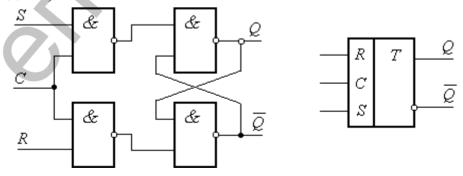

**Синхронный RS-триггер**. Известно, что из-за задержек переключения логических элементов могут возникнуть ложные состояния. Устранить это помогает временное стробирование. Временное стробирование обеспечивается синхронизирующими (тактовыми) импульсами, поэтому в синхронном RS-триггере кроме информационных входов R и S имеется вход C, на который подается синхронизирующий сигнал (рисунок S.1).

Такой триггер функционирует как RS-триггер только при условии наличия синхронизирующих сигналов. В противном случае, т.е. при отсутствии синхронизирующих сигналов, состояние его сохраняется неизменным  $Q^{n+1} = Q^n$ , какие бы сигналы ни подавались на информационные входы, причем возможна подача сочетания R = S = 1 (или R = S = 0 для триггера с инверсными входами).

Рисунок 5.1 — Синхронный *RS*-триггер с прямыми статическими входами на элементах **И-НЕ** и его условное обозначение

Специфика синхронных триггеров со статическим управлением по входу синхронизации такова, что в течение времени действия тактового сигнала, смена сигналов на информационных входах вызывает новые срабатывания триггера. Следовательно, синхронные триггеры со статическим управлением при активном состоянии тактового входаведут себя подобно асинхронным. Во многих случаях это свойство является недостатком, так как может оказаться причиной сбоев в цифровых устройствах.

D-триггеры. Функциональная особенность триггеров этого типа состоит в том, что сигнал на выходе Q в такте (n+1) равен значению сигнала на входеD в предыдущем такте n. Другими словами, D-триггер задерживает на один такт информацию, существовавшую на входе D. Триггер принял свое название от первой буквы английского слова delay — задержка.

**Т-триггеры.** Триггер T - типа, или счетный тригтер является основой всех пересчетных схем и имеет один информационный T-вход. Смена состояния такого триггера на *противоположное* происходит всякий раз, когда входной сигнал меняет свое значение в определенном направлении. В зависимости от того, какой перепад напряжения используется для управления (от нуля к единице или от единицы к нулю), различают счетные триггеры с прямым (T-триггеры) или инверсным (T-триггеры) динамическим управлением.

По способу ввода входной информации T-триггеры могут быть асинхронными и синхронными.

Особенностью T-триггера является в два раза меньшая частота выходных сигналов по сравнению с частотой сигналов на входе. Это позволяет использовать его в качестве делителя частоты последовательностиимпульсов на два, а также при создании двоичных счетчиков.

JK-триггеры. Функциональная особенность JK-триггеров состоит в том, что при всех входных комбинациях, кроме одной  $J^n$   $K^n$  1, они действуют подобно RS-триггеру, причем вход J играет роль входа S, а K-вход соответствует R-входу. При входной комбинации  $J^n$   $K^n$  1в каждом такте выходной сигнал меняет свое значение на противоположное. JK-триггеры не имеют неопределенных состояний.

### Описание работы

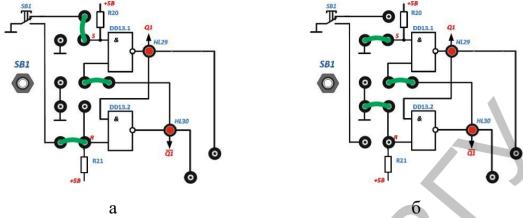

Асинхронный RS-триггер в базисе ИЛИ-НЕ

1. Собрать на панели схему, как показано на рисунке 5.2.

Рисунок 5.2 – Асинхронный RS-триггер (а и б)

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя состояние входов S и R кнопкой SB1 исследовать предлагаемую схему.

- 5. Изменяя состояние входов S и R последовательной сменой положения установки перемычек (см. рисунок 5.2 а-б) исследовать работу триггера путем составления таблицы состояний. Состояния входов изменять и отслеживать по положению перемычек (+5 или GND), состояния выходов отслеживать по светодиодам HL29, HL30. Данные занести в таблицу 5.1.

Таблица 5.1 – RS-триггер, собранный на DD13

| Bxo | ды | Выходы |                  |  |

|-----|----|--------|------------------|--|

| R   | S  | Q1     | Q <sup>-</sup> 1 |  |

| -   | _  | HL29   | HL30             |  |

| 0   | 0  |        |                  |  |

| 1   | 0  |        |                  |  |

| 0   | 0  |        |                  |  |

| 0   | 1  |        |                  |  |

| 1   | 1  |        |                  |  |

| 1   | 0  |        |                  |  |

| 1   | 1  |        |                  |  |

| 0   | 1  |        |                  |  |

6. Выключить питание. Разобрать схему.

### Синхронный RS-триггер в базисе И-НЕ

- 1. Собрать на панели схему, как показано на рисунке 5.3.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Перевести SA8 в верхнее положение (GND).

- 5. Изменяя состояние входов S и R сменой положения установки перемычек исследовать работу триггера путем составления таблицы состояний. Состояния входов R и S изменять и отслеживать по положению перемычек (+5 или GND), состояние входа C изменять нажатием кнопки SB1 и отслеживать по светодиоду HL29, состояния выходов отслеживать по светодиодам HL31, HL32. Данные занести в таблицу 5.2.

- 6. Выключить питание. Разобрать схему.

Таблица 5.2 – RS-триггер, собранный на DD22, DD23, DD24

|   | 0ДЫ | Выходы |                  |  |

|---|-----|--------|------------------|--|

| R | S   | Q2     | Q <sup>-</sup> 2 |  |

| _ | -   | HL31   | HL32             |  |

| 0 | 1   |        |                  |  |

| 1 | 0   | •      |                  |  |

| 0 | 0   |        |                  |  |

| 1 | 1   | 1      | -                |  |

| 1 | 0   |        |                  |  |

| 0 | 1   |        |                  |  |

| 0 | 0   |        |                  |  |

Рисунок 5.3 – Синхронный RS-триггер

### Счетный Т-триггер

- 1. Собрать на панели схему, как показано на рисунке 5.4.

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Перевести SA8 в верхнее положение (GND).

- 5. Состояние входа Т изменяется импульсами, поступающими от генератора 1С, состояниевыхода отслеживается по светодиоду HL31.

- 6. При необходимости изменить схему и использовать сигнал ГОИ (см. рисунок 5.1) вместо синив генератора 1С.

- 7. Выключить питание. Разобрать схему.

Рисунок 5.4 – Счетный Т-триггер

ЈК-триггер в интегральном исполнении

1. Собрать на панели схему, как показано на рисунке 5.5.

Рисунок 5.5 – ЈК-триггер

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятсяв нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя состояние входов J и K сменой положения галетного переключателя SA2 изучить работу JK-триггера в интегральном исполнении (DD26). Состояние входов отслеживать по светодиодам HL5, HL6, состояние выхода отслеживать по светодиоду HL40. Состояние входа C изменяется импульсами, поступающими от генератора 1C, при необходимости изменить схему и использовать сигнал ГОИ вместо сигнала генератора 1C.

Выключить питание. Разобрать схему.

Справочные данные. Тип микросхемы DD26: K155TB1.

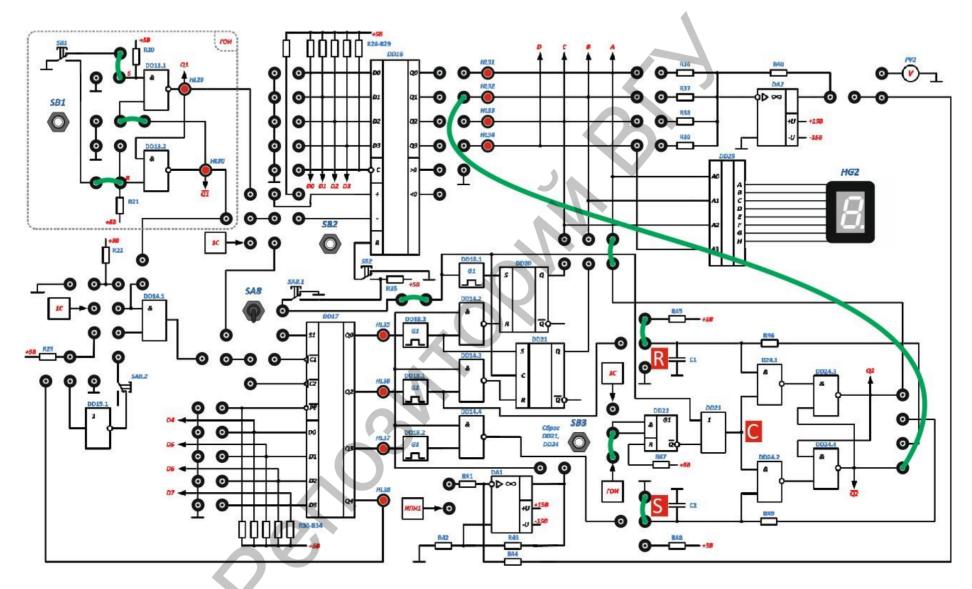

Изучение 4-разрядного регистра на базе D-триггеров в интегральном исполнении

1. Собрать на панели схему, как показано на рисунке 5.6.

Рисунок 5.6 – Схема изучения 4-разрядного регистра

- 2. Убедиться, что схема собрана правильно и на панели стенда присутствуют только необходимые для проведения данного опыта перемычки, все переключатели находятся в нижнем или крайнем левом положении. Регуляторы потенциометров R55, R56 установить в крайнее левое положение.

- 3. Включить питание стенда.

- 4. Изменяя логические уровни линий 9...12 (изменение производить сменой положения галетного переключателя SA2) изучить работу 4-х разрядного регистра в интегральном исполнении (DD29). Состояния входов DD29 отслеживать по левому разряду индикатора HG1, состояния выходов DD29 отслеживать по правому разряду индикатора HG1. Состояние линии 17 изменяется импульсами, поступающими от генератора 1С, при необходимости изменить схему и использовать сигнал ГОИ вместо сигнала генератора 1С.

Выключить питание. Разобрать схему. Справочные данные. Тип микросхемы DD29: K155TM7.

### Контрольные вопросы

- 1. Дайте определение понятию «триггер».

- 2. Какие виды триггеров вы знаете?

- 3. В чем особенность Т-триггера?

- 4. При каких условиях функционирует *RS*-триггеры?

### ЛИТЕРАТУРА

- 1. Раннев, Г.Г. Информационно-измерительная техника и электроника: учебник для студ. выш. учеб. Заведений / Г.Г. Раннев [и др.] / под. ред. Г.Г. Раннева. М.: Изд. центр «Академия», 2006. 512 с.

- 2. Китаев, Ю.В. Основы цифровой техники: учеб. пособие / Ю.В. Китаев. СПб.: СПбГУ ИТМО, 2007.-87 с.

- 3. Садов, С.В. Интегральная электроника: конспект лекций / В.С. Садов. Минск: БГУ, 2007. 130 с.

- 4. Садов, С.В. Интегральная электроника: лабораторный практикум для студентов специальностей: 1-31 04 02 «Радиофизика», 1-31 04 03 «Физическая электроника», 1-31 04 04 «Аэрокосмические радиоэлектронные и информационные системы и технологии», 1-98 01 01 «Компьютерная безопасность (по направлениям)», 1-31 03 07 «Прикладная информатика (по направлениям)» / В.С. Садов, Н.Н. Щетько. Минск: БГУ, 2014. 48 с.

### Учебное издание

### ИНТЕГРАЛЬНАЯ ЭЛЕКТРОНИКА

Методические рекомендации по выполнению лабораторных работ

#### Составители:

ШИЁНОК Юрий Владимирович САПЕЛКО Татьяна Ивановна ЛЮДЫНО Артур Андреевич

Технический редактор Компьютерный дизайн Г.В. Разбоева

Л.Р. Жигунова

Подписано в печать .2021. Формат  $60x84^{-1}/_{16}$ . Бумага офсетная. Усл. печ. л. 2,56. Уч.-изд. л. 2,74. Тираж экз. Заказ .

Издатель и полиграфическое исполнение — учреждение образования «Витебский государственный университет имени П.М. Машерова».

Свидетельство о государственной регистрации в качестве издателя, изготовителя, распространителя печатных изданий  $N_{\rm M} 1/255$  от 31.03.2014.

Отпечатано на ризографе учреждения образования «Витебский государственный университет имени П.М. Машерова». 210038, г. Витебск, Московский проспект, 33.